Teensy 4.1 avec kit de vente au détail de têtes de réseau

48,00 €

TVA incluse zzgl. Versandkosten

Lieferzeit: DHL Versand - 2-3 Geschäftstage in D, EU länger !

3 en stock

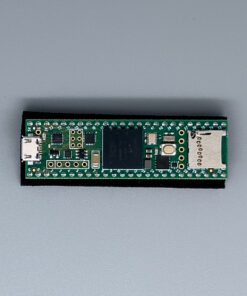

Teensy 4.1 avec kit de vente au détail de headers PJRC

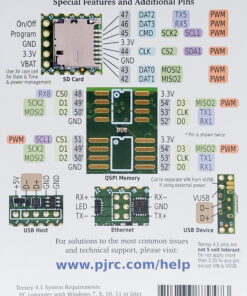

Le nouveau Teensy 4.1 est doté d’un processeur ARM Cortex-M7 cadencé à 600 MHz, d’une puce NXP iMXRT1062, d’une mémoire flash quatre fois plus grande que celle du Teensy 4.0 et de deux emplacements de mémoire supplémentaires pour étendre la mémoire. Il a la même taille et la même forme que le Teensy 3.6 (2,4 x 0,7 pouces) et offre une plus grande capacité d’E/S, Ethernet-PHY, un socle pour carte SD et un port hôte USB.

Lorsqu’il fonctionne à pleine charge, le Teensy 4.1 consomme environ 100 mA et offre un support pour la mise à l’échelle dynamique de l’horloge.

Détails techniques

- ARM-Cortex-M7 à 600MHz

- 1024K de RAM (512K sont étroitement couplés)

- 128Mb Flash (64K réservés à la restauration &Amp ; émulation EEPROM)

- Port hôte USB

- 2x emplacements de mémoire flash supplémentaires

- 3x CAN-Bus (1 avec CAN FD)

- 2x I2S audio numérique

- 1x S/PDIF audio numérique

- 1x SDIO (4 bits) natif SD

- 3x SPI, tous avec 16 mots FIFO

- 3x I2C, tous avec 4 octets FIFO

- 7x série, tous avec 4 octets FIFO

- 32x canaux DMA à usage général

- 31x broches PWM

- 40x broches numériques, toutes compatibles avec les interruptures

- 14x broches analogiques, 2 ADC sur la puce

- Accélération cryptographique

- Générateur de nombres aléatoires

- RTC pour la date/l’heure

- FlexIO programmable

- Pipeline de traitement des pixels

- Déclenchement croisé périphérique

- Ethernet PHY

- Socle pour carte microSD

- Gestion de l’alimentation on/off

Vous trouverez des informations plus détaillées dans la fiche technique sous « Fiches techniques » ou sur le site du fabricant https://www.pjrc.com/teensy/

Remarque:

Les entrées de signal de Teensy ne sont pas conçues pour des tensions allant jusqu’à 3,3V.

| Poids | 0,2 kg |

|---|

Produits similaires

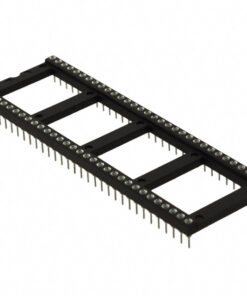

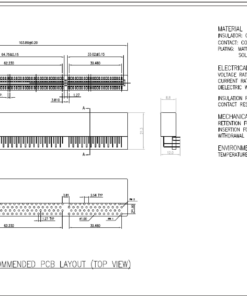

Composants, socles et éléments de construction

TVA incluse

zzgl. Versandkosten

Lieferzeit: DHL Versand - 2-3 Geschäftstage in D, EU länger !

Amiga 1200

TVA incluse

zzgl. Versandkosten

Lieferzeit: DHL Versand - 2-3 Geschäftstage in D, EU länger !

Composants, socles et éléments de construction

TVA incluse

zzgl. Versandkosten

Lieferzeit: DHL Versand - 2-3 Geschäftstage in D, EU länger !

Composants, socles et éléments de construction

TVA incluse

zzgl. Versandkosten

Lieferzeit: DHL Versand - 2-3 Geschäftstage in D, EU länger !

Composants, socles et éléments de construction

TVA incluse

zzgl. Versandkosten

Lieferzeit: DHL Versand - 2-3 Geschäftstage in D, EU länger !

Composants, socles et éléments de construction

TVA incluse

zzgl. Versandkosten

Lieferzeit: DHL Versand - 2-3 Geschäftstage in D, EU länger !