Kit de venta al público Teensy 4.1 con cabezales

48,00 €

IVA incl. zzgl. Versandkosten

Lieferzeit: DHL Versand - 2-3 Geschäftstage in D, EU länger !

3 disponibles

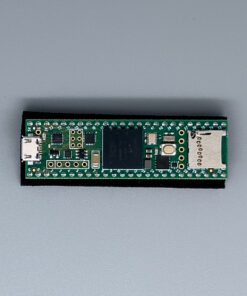

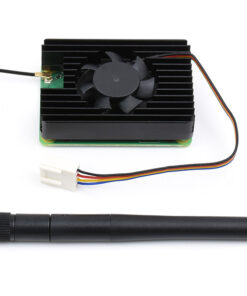

Teensy 4.1 con cabezales de PJRC Retail Kit

El nuevo Teensy 4.1 tiene un procesador ARM Cortex-M7 a 600 MHz, un chip NXP iMXRT1062, cuatro veces más memoria flash que el Teensy 4.0 y dos ranuras de memoria adicionales para ampliar la memoria. Tiene el mismo tamaño y forma que el Teensy 3.6 (2,4 x 0,7 pulgadas) y ofrece una mayor capacidad de E/S, Ethernet PHY, conector para tarjetas SD y conexión USB host.

Cuando funciona a plena carga, el Teensy 4.1 requiere aproximadamente 100 mA de corriente y ofrece soporte para el escalado dinámico del reloj.

Detalles técnicos

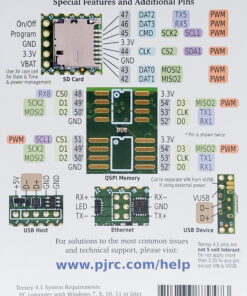

- ARM-Cortex-M7 a 600MHz

- 1024K RAM (512K están muy acoplados)

- 128Mb Flash (64K reservados para recuperación & amp; emulación EEPROM)

- Puerto USB host

- 2 ranuras de memoria flash adicionales

- 3x bus CAN (1 con CAN FD)

- 2x I2S Audio Digital

- 1x audio digital S/PDIF

- 1x SDIO (4 bits) nativa SD

- 3x SPI, todos con FIFO de 16 palabras

- 3x I2C, todos con FIFO de 4 bytes

- 7x serie, todas con FIFO de 4 bytes

- 32x canales DMA de propósito general

- 31x pines PWM

- 40x pines digitales, todos con capacidad de interrupción

- 14x pines analógicos, 2 ADC en el chip

- Aceleración criptográfica

- Generador de números aleatorios

- RTC para fecha/hora

- FlexIO programable

- Proceso de píxeles

- Disparo cruzado periférico

- PHY Ethernet

- Toma para tarjeta microSD

- Activación/desactivación de la gestión de energía

Encontrarás información más detallada en la ficha técnica en «Fichas técnicas» o en el sitio web del fabricante https://www.pjrc.com/teensy/.

Nota

Las entradas de señal del Teensy no sólo sirven para tensiones de hasta 3,3 V.

| Peso | 0,2 kg |

|---|

Productos relacionados

IVA incl.

zzgl. Versandkosten

Lieferzeit: DHL Versand - 2-3 Geschäftstage in D, EU länger !

Amiga 1200

IVA incl.

zzgl. Versandkosten

Lieferzeit: DHL Versand - 2-3 Geschäftstage in D, EU länger !